# Zur Realisierbarkeit des PRAM Modelles

Dissertation

zur Erlangung des akademischen Grades

des Doktors der Naturwissenschaften

der Technischen Fakultät

der Universität des Saarlandes

vorgelegt

von

Jörg Keller

6600 Saarbrücken 1992 Tag des Kolloquiums: 27. Mai 1992

Dekan: Prof. Dr. R. Maurer

Berichterstatter: Prof. Dr. W.J. Paul

Prof. Dr. J. Buchmann

### Vorwort

Der Ursprung dieser Arbeit liegt in einer Aufgabe, die mir Herr Prof. Paul im Spätherbst 1989 zuteilte: der Entwurf eines Prozessors, der mehrere Instruktionströme in einer Pipeline verarbeitet. Ihm danke ich für seine Betreuung und Unterstützung und für sein unerschütterliches Vertrauen.

Das hier vorgestellte Ergebnis sieht anders aus als damals erwartet, es verdankt seine Gestalt einer kontinuierlichen Entwicklung und Veränderung. Diese Entwicklung fand nicht im stillen Kämmerlein statt. Sie profitierte vom Aufeinanderprallen verschiedener Meinungen, vielfachem Überdenken und Überarbeiten von bereits als endgültig angesehenen Fakten und vielen Diskussionen innerhalb und außerhalb des Fachbereiches.

Ich danke Prof. Friedhelm Meyer auf der Heide, Herrn Dr. Martin Dietzfelbinger, Herrn Dr. Torben Hagerup, Herrn Dr. Helmut Seidl, Herrn Georg Sander und allen Mitarbeitern des Instituts für Rechnerarchitektur für ihr reges Interesse, ihre Kritik und ihre Anregungen.

Eine weitere Arbeit aus dem großen Gebiet der PRAM entstand im gleichen Zeitraum. Herrn Ferri Abolhassan, meinem Partner und Zimmergenossen, danke ich für eine gelungene Zusammenarbeit ohne Konkurrenzdenken.

Herrn Curd Engelmann, der im Rahmen seiner Diplomarbeit wesentliche Teile der Simulationssoftware implementierte, danke ich für seine Geduld und seine Mühe, alle Änderungen des Modells in die Simulation zu übertragen.

Frau Stefanie Urig danke ich für ihre Nachsicht gegenüber unberechenbaren Arbeitszeiten und Fällen von geistiger Versunkenheit in irgendwelchen PRAM Problemen.

Meinen Eltern danke ich für die finanzielle Unterstützung in den Jahren meiner Ausbildung, ohne die die vorliegende Arbeit nicht möglich gewesen wäre.

Sulzbach, im Februar 1992

Jörg Keller

# Inhaltsverzeichnis

| 1                   | Ein                            | leitung            | g — Vom Abacus zur PRAM           | 1   |

|---------------------|--------------------------------|--------------------|-----------------------------------|-----|

| 2                   | Parallelrechner in der Theorie |                    |                                   |     |

| 2.1 Das PRAM Modell |                                |                    | RAM Modell                        | 5   |

|                     |                                | 2.1.1              | Definitionen und Notationen       | 5   |

|                     |                                | 2.1.2              | Programmierung von PRAMs          | 7   |

|                     |                                | 2.1.3              | Realisierungsansätze              | 9   |

|                     | 2.2                            | Theore             | etische Vorarbeiten               | 10  |

|                     |                                | 2.2.1              | Verteilen des globalen Speichers  | 10  |

|                     |                                | 2.2.2              | Verbindungsstrukturen             | 13  |

|                     |                                | 2.2.3              | Einige Netzwerke                  | 15  |

|                     |                                | 2.2.4              | Routingalgorithmen                | 16  |

|                     | 2.3                            | Die Fl             | uent Machine                      | 17  |

|                     |                                | 2.3.1              | Verteilung des globalen Speichers | 17  |

|                     |                                | 2.3.2              | Routing                           | 18  |

|                     |                                | 2.3.3              | Konkurrierende Zugriffe           | 19  |

|                     |                                | 2.3.4              | Ghost Pakete                      | 20  |

|                     |                                | 2.3.5              | Rückweg                           | 21  |

|                     |                                | 2.3.6              | Aufbau                            | 22  |

| 3                   | D                              | wontur             | g van Rechnern                    | 23  |

|                     |                                | v — r i. i i i i i | y viii neriilerii                 | 7.0 |

|   | 3.1        | Forma   | ıles Modell                           | 23 |

|---|------------|---------|---------------------------------------|----|

|   |            | 3.1.1   | Hochsprache und Compiler              | 25 |

|   |            | 3.1.2   | Hardware                              | 25 |

|   | 3.2        | Änder   | ungen des Modells                     | 32 |

|   | 3.3        | Wicht   | ige Hardware Bausteine                | 33 |

|   |            | 3.3.1   | Multiplexer                           | 33 |

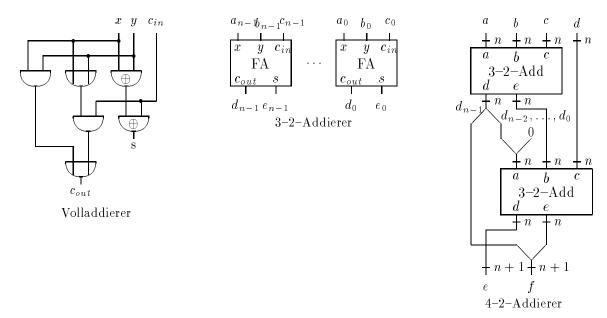

|   |            | 3.3.2   | Addierer                              | 34 |

|   |            | 3.3.3   | Subtrahierer                          | 35 |

|   |            | 3.3.4   | Inkrementierer                        | 35 |

|   |            | 3.3.5   | Vergleicher                           | 35 |

|   |            | 3.3.6   | Multiplizierer                        | 36 |

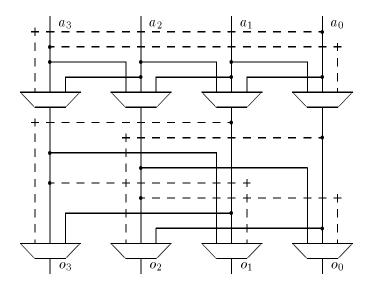

|   |            | 3.3.7   | Rotierer und Shifter                  | 39 |

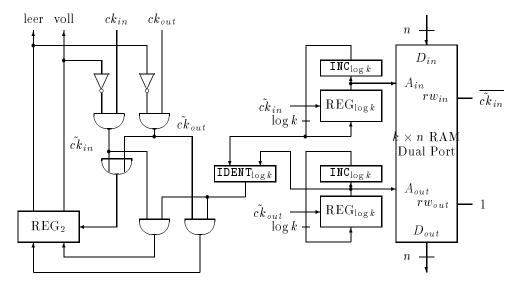

|   |            | 3.3.8   | FIFO-Schlange                         | 41 |

|   | 3.4        | Bewer   | tung der Fluent Machine               | 42 |

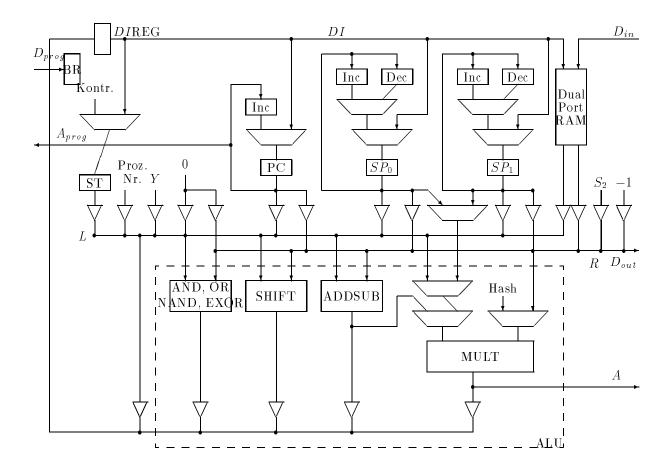

|   |            | 3.4.1   | Maschinensprache und Prozessor        | 43 |

|   |            | 3.4.2   | Netzwerk                              | 48 |

|   |            | 3.4.3   | Analyse                               | 51 |

|   | <b>1</b> 7 | änderu  |                                       | 53 |

| Ė | ver        |         |                                       | 99 |

|   | 4.1        | Pipelii | ning                                  | 53 |

|   |            | 4.1.1   | Virtuelle Prozessoren                 | 55 |

|   |            | 4.1.2   | Sortierfelder                         | 57 |

|   |            | 4.1.3   | Änderungen des Routingalgorithmus     | 59 |

|   | 4.2        | Delaye  | ed LOAD                               | 60 |

|   | 4.3        | Simula  | ationen                               | 61 |

|   |            | 4.3.1   | Einfluß von Hashing                   | 61 |

|   |            | 4.3.2   | Bestimmung der Konstanten $c$ und $z$ | 62 |

|   | 4.4 | Analy   | se der Änderungen                                    | 63 |

|---|-----|---------|------------------------------------------------------|----|

|   |     | 4.4.1   | Änderung der Hardwarekosten                          | 63 |

|   |     | 4.4.2   | Änderung des Zeitverhaltens                          | 64 |

|   |     | 4.4.3   | Vergleich der Maschinen                              | 65 |

| 5 | Des | sign Va | arianten                                             | 67 |

|   | 5.1 | Unters  | stützung konkurrierender Zugriffe                    | 68 |

|   |     | 5.1.1   | Konstruktion einer EREW PRAM                         | 68 |

|   |     | 5.1.2   | Simulation konkurrierender Zugriffe                  | 70 |

|   |     | 5.1.3   | Analyse                                              | 72 |

|   |     | 5.1.4   | Einfluß auf CREW                                     | 72 |

|   | 5.2 | Unters  | stützung paralleler Präfixberechnung                 | 74 |

|   |     | 5.2.1   | Definition und Eigenschaften                         | 74 |

|   |     | 5.2.2   | Hardware für Multipräfix                             | 74 |

|   |     | 5.2.3   | Hardware-MP versus Software-MP                       | 76 |

|   |     | 5.2.4   | Einschränkungen                                      | 77 |

|   |     | 5.2.5   | Anwendungen von Multipräfix und Sync                 | 78 |

|   | 5.3 | Simula  | ation großer Prozessorzahlen                         | 82 |

|   |     | 5.3.1   | Kontextwechsel                                       | 83 |

|   |     | 5.3.2   | Unterstützende Hardware für schnellen Kontextwechsel | 84 |

|   |     | 5.3.3   | Unterstützende Hardware für mehrere Kontexte         | 85 |

|   |     | 5.3.4   | Kombination beider Ansätze                           | 85 |

|   |     | 5.3.5   | Analyse                                              | 86 |

|   | 5.4 | Bewer   | tung am Beispiel                                     | 90 |

|   |     | 5.4.1   | Berechnung von Zusammenhangskomponenten              | 90 |

|   |     | 5.4.2   | Analyse und Messungen                                | 91 |

|   |     | 5.4.3   | Abschätzung der Anzahl von Kontextwechseln           | 93 |

| 6                 | Ent                          | Entwurf eines Prototyps        |                              |     |  |

|-------------------|------------------------------|--------------------------------|------------------------------|-----|--|

| 6.1 Der Prozessor |                              |                                |                              |     |  |

|                   | 6.2                          |                                |                              |     |  |

|                   | 6.3                          |                                |                              |     |  |

|                   |                              | 6.3.1                          | Größe von PCBs               | 107 |  |

|                   |                              | 6.3.2                          | On-Board und Off-Board Links | 107 |  |

|                   |                              | 6.3.3                          | Anordnung von Boards         | 109 |  |

|                   |                              | 6.3.4                          | Eine Alternative             | 115 |  |

|                   | 6.4                          | Anbino                         | dung an die Außenwelt        | 116 |  |

| 7                 | Zus                          | ammei                          | nfassung                     | 117 |  |

| Li                | Literaturverzeichnis 11      |                                |                              |     |  |

| Aı                | Anhang 1                     |                                |                              |     |  |

| A                 | Cod                          | Code für Bitonisches Sortieren |                              |     |  |

| В                 | Kontrolle der Fluent Machine |                                |                              | 127 |  |

|                   | B.1                          | Kontro                         | ollsignale des Prozessors    | 127 |  |

|                   | R 2                          | Kontro                         | ollsignale des Netzknotens   | 130 |  |

# Abbildungsverzeichnis

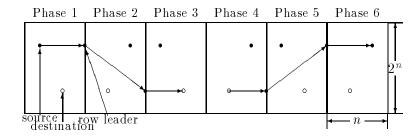

| 2.1 | 6 Phasen Routing der Fluent Machine                                               | 19 |

|-----|-----------------------------------------------------------------------------------|----|

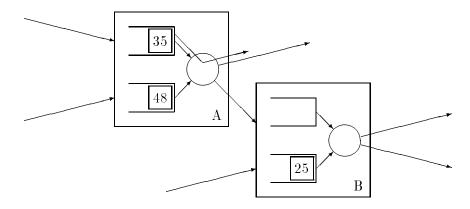

| 2.2 | Funktion von Ghost Paketen                                                        | 21 |

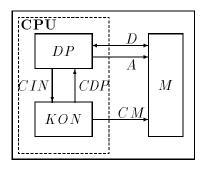

| 3.1 | Grobstruktur der Hardware                                                         | 26 |

| 3.2 | Multiplexer                                                                       | 33 |

| 3.3 | Volladdierer, 3–2–Addierer, 4–2–Addierer                                          | 38 |

| 3.4 | Rotierer und Shifter für 4-bit Zahlen                                             | 41 |

| 3.5 | Aufbau einer FIFO Schlange                                                        | 42 |

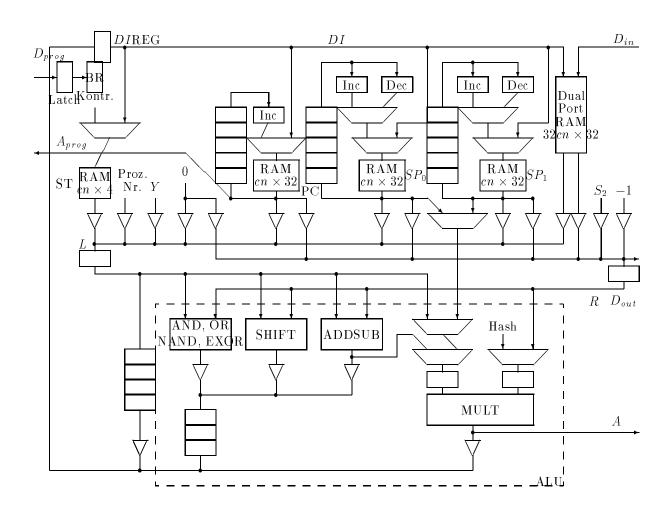

| 3.6 | Datenpfade des Prozessors                                                         | 45 |

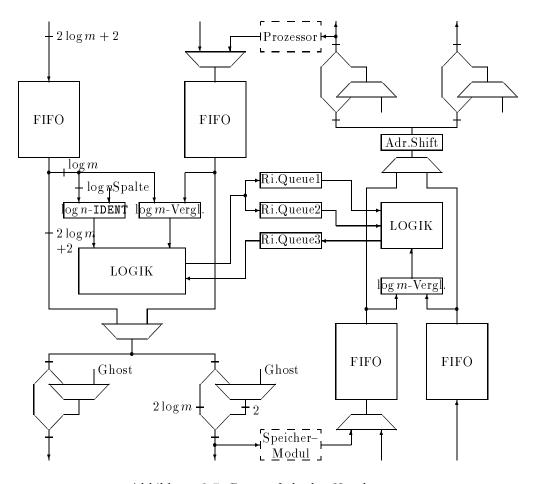

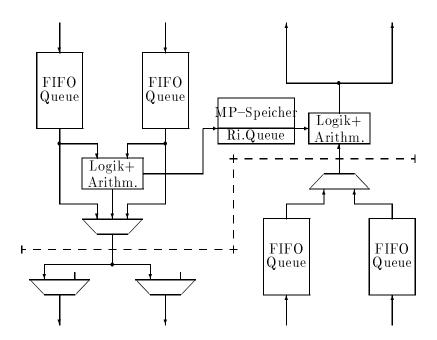

| 3.7 | Datenpfade des Netzknotens                                                        | 49 |

| 4.1 | Datenpfade des veränderten Prozessors                                             | 56 |

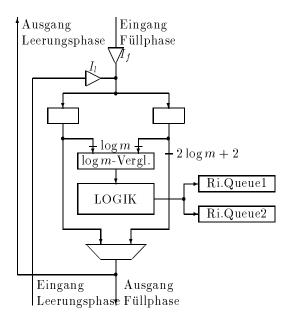

| 4.2 | Datenpfade des Sortierknotens der Phase 1                                         | 58 |

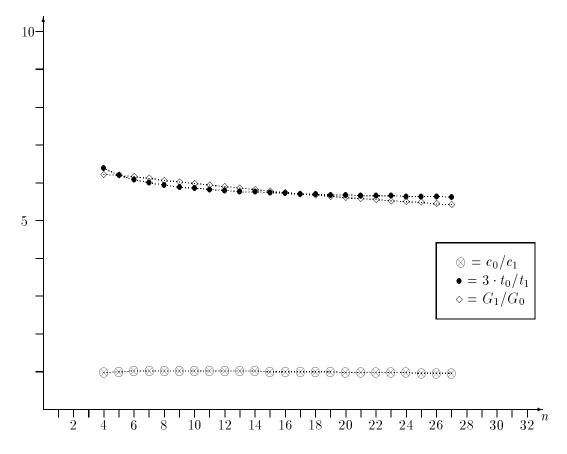

| 4.3 | Quotienten der Kosten, Zeit- und Gütenfunktionen                                  | 66 |

| 5.1 | Bitonischer Sortier Algorithmus                                                   | 71 |

| 5.2 | Minimal notwendiger Anteil von konkurrierendem Zugriff                            | 73 |

| 5.3 | Minimal notwendiger Anteil von Multipräfix und Sync                               | 78 |

| 5.4 | Synchronisierung von Prozessoren                                                  | 80 |

| 5.5 | Datenpfade zum Wechseln von Kontexten                                             | 86 |

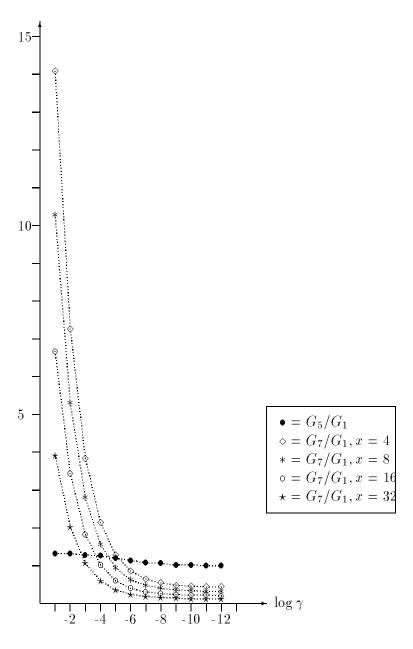

| 5.6 | Quotienten der Gütenfunktionen von D7 und D6 in Abhängigkeit von $\boldsymbol{x}$ | 88 |

| 5.7 | Quotienten der Gütenfunktionen                                                    | 89 |

| 5.8 | Programm für Zusammenhangskomponenten          | 92  |

|-----|------------------------------------------------|-----|

| 6.1 | Auslastung der Busse vom und zum Prozessorchip | 97  |

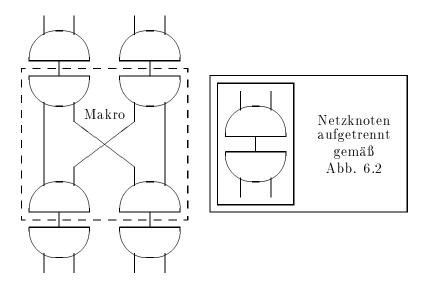

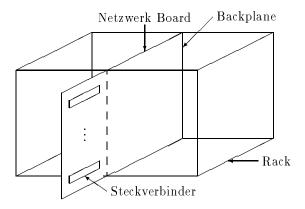

| 6.2 | Schnitt durch Netzwerkknoten                   | 102 |

| 6.3 | Aufteilung von Netzwerkknoten für $x=1$        | 103 |

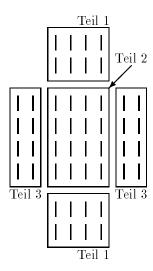

| 6.4 | Anordnung von Boards nach Wise                 | 111 |

| 6.5 | Anordnung der Boards in 3 Teilen               | 114 |

| 6.6 | Anordnung von Steckverbindern auf Boards       | 115 |

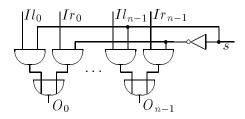

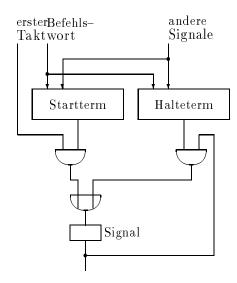

| B.1 | Berechnung eines Kontrollsignales              | 128 |

| В 9 | Instruktionsformato                            | 198 |

# **Tabellenverzeichnis**

| 3.1 | Delay der Grundbausteine                                  | 30  |

|-----|-----------------------------------------------------------|-----|

| 3.2 | Basiskosten der Grundbausteine                            | 31  |

| 3.3 | Packungsfaktoren                                          | 31  |

| 3.4 | Befehlssatz                                               | 44  |

| 3.5 | Aufteilung der Kosten des Prozessors                      | 47  |

|     |                                                           |     |

| 6.1 | Benötigte Anzahlen von Netzwerkchips                      | 101 |

| 6.2 | Anzahl von Slices bei Halbierung der Links                | 104 |

| 6.3 | Benötigte Anzahlen von Netzwerkchips bei halbierten Links | 105 |

| 6.4 | Größe von Subnetzwerken auf PCBs                          | 107 |

| 6.5 | Notwendige Kabel bei verschiedenen Partitionierungen      | 108 |

| 6.6 | Notwendige Kabel in Off-Board Links                       | 109 |

| 6.7 | Knoten in Subnetzwerk $j$                                 | 112 |

| 6.8 | Zuordnung Subnetzwerk zu Knoten u                         | 112 |

## Kapitel 1

# Einleitung — Vom Abacus zur PRAM

Schon seit vielen Jahrhunderten versucht der Mensch, Berechnungen aller Arten zu beschleunigen. Bereits 500 Jahre vor Beginn unserer Zeitrechnung beginnt dieses Streben mit der Erfindung des Abacus und zieht sich über die Addiermaschinen des 17. Jahrhunderts bis zu den Computern heutiger Tage. Mit der Leistungssteigerung der Rechenmaschinen ging aber stets ein Anwachsen der zu verarbeitenden Datenmenge einher. Waren es zuerst nur einzelne Rechnungen zur Steuereintreibung oder zur Erstellung von Logarithmentafeln, die man zur Standortbestimmung von Schiffen benötigte, so berechnet man in unserem Jahrhundert Statistiken aus Milliarden von Daten und simuliert komplizierte physikalische Vorgänge.

Diesem Wunsch nach Leistungssteigerung versuchten Rechnerarchitekten stets Rechnung zu tragen. Ging die Entwicklung von Computern zuerst dahin, Rechner mit immer schnellerer Zentraleinheit und immer mächtigerem Befehlssatz zu bauen, so suchte man bereits in den siebziger Jahren nach anderen Wegen zur Leistungssteigerung: man begann mit der Entwicklung von Vektor- und Parallelrechnern. Erstere beschleunigen vorwiegend numerische Rechnungen durch Überlappung von komplizierten (und zeitintensiven) Operationen mit Fließkommazahlen; Beispiele sind Cray XMP [Cra84] und IBM SPARK [FOP<sup>+</sup>92]. Letztere versuchen Berechnungen verschiedenster Art durch den gleichzeitigen Einsatz mehrerer Prozessoren zu beschleunigen. Auch Kombinationen, bei denen jeder Prozessor eines Parallelrechners ein Vektorcomputer ist, sind denkbar und existieren, so zum Beispiel der SUPRENUM Rechner [Tro88].

Jeder Prozessor eines Parallelrechners ist mit einigen wenigen anderen Prozessoren fest verbunden und kann über diese Verbindungen Daten mit ihnen austauschen. Nicht jede Verbindungsstruktur ist allerdings für alle Probleme geeignet. Zum Beispiel ist das Shuffle-Exchange-Netz zum Sortieren, der Torus zum Multiplizieren von Matrizen sehr gut geeignet, jedoch nicht notwendigerweise umgekehrt. In diesem Sinne sind die existierenden Parallelrechner Spezialrechner. Die Übertragung paralleler Algorithmen zwischen Parallelrechnern

mit unterschiedlicher Verbindungsstruktur ist oft nicht möglich oder zumindest aufwendig. Teilweise ist die Verbindungsstruktur auch nicht zur Skalierung auf größere Prozessorzahlen geeignet. Beispiele hierfür sind Verbindungsstrukturen wie Busse oder vollständig verbundene Graphen. Deshalb suchte man nach einem parallelen Äquivalent zum von-Neumann-Rechner, einem "general purpose parallel computer". Erste Veröffentlichungen hierzu stammen von Schwartz [Sch80] und Galil und Paul [GP83].

Die theoretische Informatik liefert ein solches Modell, die sogenannte PRAM (parallel random access machine). Hierbei arbeiten N Prozessoren synchron auf einem gemeinsamen globalen Speicher. Man erhält so ein sehr einfaches und komfortables Programmiermodell, das die Benutzung beliebiger Verbindungsstrukturen erlaubt. Die heute verfügbare Technologie erlaubt allerdings nicht, Speicherelemente zu bauen, die beliebig viele gleichzeitige Zugriffe in konstanter Zeit bearbeiten können. Existierende Parallelrechner mit globalem Speicher wie der ALLIANT FX/8 [PM86] haben nur wenige Prozessoren und können auch nicht weiter skaliert werden. Deshalb suchte man nach Möglichkeiten, eine PRAM auf einem Parallelrechner mit fester Verbindungsstruktur effizient zu simulieren. Hierzu gibt es mittlerweise einige Ansätze. Das Ziel dieser Arbeit ist es, diese Ansätze auf ihre Realisierbarkeit hin zu prüfen und so die "beste" PRAM Realisierung zu finden.

Um allerdings von einer "besten" Maschine reden zu können, benötigt man ein genaues und faires Vergleichsmaß. Bei der Bewertung eines Rechners sind in diesem Zusammenhang die wichtigsten Kriterien Preis und Leistung, ein einfaches Maß ist das Preis-Leistungs-Verhältnis. Schwierig ist die Festlegung der Einheiten für Preis und Leistung. Ein Preis in Dollar oder Deutscher Mark ist unangebracht, da er neben Materialkosten auch Löhne, Verwaltungs- und Entwicklungskosten berücksichtigen muß und zusätzlich noch vielen äußeren Faktoren wie Schwankungen der Umrechungskurse oder der Verfügbarkeit von Teilen abhängt. Ebenso sind für die Leistung Einheiten wie Instruktionen pro Sekunde oder Fließkommaoperationen pro Sekunde nicht geeignet. Sie hängen zu sehr vom speziellen Programm und vom Befehlssatz der Maschine ab. Außerdem sollte das gewählte Vergleichsmaß schnell "von Hand" zu berechnen sein, also ohne die geplante Maschine zu bauen oder aufwendige Simulationen durchführen zu müssen. Müller und Paul entwickelten 1990 ein solches Maß, das geeignet scheint.

Die vorliegende Arbeit ist wie folgt gegliedert. Kapitel 2 beschreibt das PRAM Modell als theoretisches paralleles Programmiermodell und gibt einen kurzen Überblick über Ansätze zu seiner Realisierung. Theoretische Vorarbeiten der Bereiche Hashing und Routing werden skizziert und verglichen. Der favorisierte Ansatz wird detailliert beschrieben. Kapitel 3 stellt das oben erwähnte formale Modell zum Bewerten und Vergleichen von Rechnern vor, beschreibt notwendige Änderungen beim Übergang zu Parallelrechnern und stellt die in dieser Arbeit verwendeten Hardware Komponenten vor. Als Beispiel wird eine Hardware für obigen Ansatz im Detail entwickelt und bewertet. In Kapitel 4 wird obiger Ansatz "ingenieursmäßig" überarbeitet, um die konstanten Faktoren in der Bewertung zu verbessern. Eine Analyse zeigt die Auswirkungen der Veränderungen und den Grad der Verbesserung. In Kapitel 5 werden verschiedene Designvarianten vorgestellt und diskutiert: konkurrierender

Zugriff, parallele Präfixberechnung und Kontextwechsel. Bei allen diesen Varianten stellt sich die Frage, ob eine Unterstützung in Hardware notwendig ist oder ob eine Simulation in Software genügt. Die Antworten auf diese Fragen geben auch Aufschluß darüber, welche dieser Eigenschaften des original Ansatzes essentiell sind und welche lediglich schmückendes Beiwerk sind. Kapitel 6 beschreibt einen möglichen Prototyp nach heutigem Stand der Technologie. Der Schwerpunkt liegt auf dem Übergang vom theoretischen Modell zur kommerziell verfügbaren und finanzierbaren Technik.

## Kapitel 2

## Parallelrechner in der Theorie

Mit dem Aufkommen der ersten Überlegungen zum Bau von Parallelrechnern Ende der siebziger Jahre wurde auch die theoretische Informatik auf diese Rechner aufmerksam. Man benötigte ein ideales Modell eines Parallelrechners — ähnlich der Random Access Machine im sequentiellen Fall —, das es erlaubte, die Komplexität von Algorithmen zu bestimmen, ohne von einer speziellen existierenden Maschine direkt beeinflußt zu werden. Dieses Modell muß deshalb eine sehr einfache Verbindungsstruktur aufweisen. FORTUNE und WYLLIE definierten in [FW78] ein solches Modell und nannten es parallel random access machine oder abgekürzt PRAM. Auch andere Forscher definierten ähnliche Modelle, zum Beispiel LEV, PIPPENGER und VALIANT in [LPV81], in [FW78] wurde das Modell jedoch meines Wissens erstmalig definiert und zur Komplexitätsbestimmung benutzt.

#### 2.1 Das PRAM Modell

#### 2.1.1 Definitionen und Notationen

**Definition 2.1** Eine Parallel Random Access Machine (PRAM) besteht aus einer Menge von Prozessoren  $P_0, \ldots, P_{N-1}$ , und einem globalen Speicher der Größe M. Ein Prozessor ähnelt weitestgehend einer random access machine wie sie in [AHU74] definiert wird. Er führt in einem Schritt entweder eine interne Operation aus, liest ein Wort aus dem globalen Speicher oder schreibt ein Wort in den globalen Speicher. Ein Schritt hat feste konstante Länge.

In einigen Arbeiten, z.B. bei KARP und RAMACHANDRAN [KR90], wird zusätzlich jedem Prozessor ein lokaler Speicher zugeordnet, auf den nur er allein zugreifen kann. Der Zugriff auf lokalen Speicher gehört zu den internen Operationen.

Greifen im gleichen Schritt mehrere Prozessoren auf eine Zelle des globalen Speichers zu, so kommt es zu Konflikten. Zur Regelung dieser Konflikte müssen Konventionen getroffen werden. Verschiedene Konventionen definieren verschiedene PRAM Modelle. Eine gemeinsame Konvention aller Modelle ist, daß in einem Schritt auf eine Zelle nur lesend oder nur schreibend zugegriffen wird. Einige Arbeiten umgehen dieses Problem, indem sie jeden Schritt als zwei Halbschritte auffassen, wobei im ersten Halbschritt alle Leseoperationen und im zweiten Halbschritt alle Schreiboperationen abgewickelt werden. Die wichtigsten Modelle sollen hier kurz vorgestellt werden. Die Nomenklatur der Modelle wurde aus [MV84] und [DR86] übernommen.

- Im exclusive read exclusive write (EREW) Modell darf eine Zelle in einem Schritt von höchstens einem Prozessor gelesen oder geschrieben werden. Dieses Modell wurde in [LPV81] eingeführt.

- Im concurrent read exclusive write (CREW) Modell darf eine Zelle in einem Schritt von mehreren Prozessoren gelesen oder von einem geschrieben werden. Dies ist das ursprüngliche Modell aus [FW78].

- Im concurrent read concurrent write (CRCW) Modell darf eine Zelle in einem Schritt von mehreren Prozessoren gelesen oder von mehreren geschrieben werden.

- Im concurrent read owner write (CROW) Modell darf eine Zelle in einem Schritt von mehreren Prozessoren gelesen oder von einem bestimmten Prozessor, ihrem "owner" geschrieben werden. Dieses Modell wurde in [DR86] eingeführt.

Weitere Kombinationen von Lese- und Schreibrechten sind denkbar. Einige werden verwandt, das Modell der ERCW (exclusive read concurrent write) PRAM hingegen wurde meines Wissens bisher nirgends benutzt.

In den Modellen, die concurrent write benutzen, muß zusätzlich festgelegt werden, welchen Wert eine Zelle erhält, die in einem Schritt von mehreren Prozessoren geschrieben wird. Drei Hauptkonventionen werden verwandt.

- Im arbitrary Modell gewinnt einer der schreibenden Prozessoren, aber es kann nicht vorhergesagt werden, welcher.

- Im *common* Modell müssen alle Prozessoren, die in einem Schritt eine Zelle schreiben, den gleichen Wert schreiben.

- Im *priority* Modell gibt es eine injektive Abbildung von Prozessornummern in die natürlichen Zahlen. Schreiben mehrere Prozessoren im gleichen Schritt die gleiche Zelle, so übernimmt die Zelle den Wert des Prozessors, der bezüglich obiger Funktion den größten Wert hat.

Die Mächtigkeit der obigen Modelle war und ist Gegenstand von komplexitätstheoretischen Untersuchungen. Als Maß der Komplexität eines Problems der Größe n nimmt man die

Anzahl der benötigten Prozessoren p(n) und die benötigte Zeit t(n). Man bezeichnet parallele Algorithmen dann als *optimal*, wenn sie  $p(n) \cdot t(n) = O(T_s(n))$  erfüllen, wobei  $T_s(n)$  die asymptotische Laufzeit des schnellsten bekannten sequentiellen Algorithmus für das gleiche Problem mit Größe n ist.

#### 2.1.2 Programmierung von PRAMs

Zum Beschreiben von Algorithmen für PRAMs benutzt man eine sequentielle von-Neumann Programmiersprache wie PASCAL. Die Benutzung von Parallelität erfolgt durch die zusätzliche Anweisung

```

for x \in X pardo A(x) od

```

X ist eine Menge und die Abarbeitung der Anweisung beinhaltet die Schritte

- 1. Ordne jedem x aus X einen Prozessor zu

- 2. Führe auf allen diesen Prozessoren gleichzeitig die Anweisungsfolge A(x) aus.

Die Anweisungen werden synchron ausgeführt. Das parallele Konstrukt ist also erst beendet, wenn alle Prozessoren A(x) abgearbeitet haben. Auf eine genaue Beschreibung der Semantik soll hier verzichtet werden. Zwei Beispiele dienen zur Verdeutlichung. Eine Programmiersprache für PRAMs namens FORK wurde 1990 an der Universität des Saarlandes entwickelt [HSS91] und wird gerade für eine abstrakte parallele Maschine, die weitestgehend einem Simulator des in Kapitel 6 beschriebenen Prototyps entspricht, implementiert.

- **Beispiel 1:** Sei a[1..n] ein Feld mit n verschiedenen Zahlen. Das folgende Programm berechnet das Maximum und legt es in der Variable erg ab. Das Feld b aus n Zahlen dient zur Aufnahme von Zwischenergebnissen. Es gilt t(n) = O(1) und  $p(n) = n^2$ . Der Algorithmus stammt aus [GR88].

- (1) for  $i \in \{1..n\}$  pardo b[i] := 0 od;

- (2) for  $(i_1, i_2) \in \{1..n\} \times \{1..n\}$  pardo

- (3) if  $a[i_1] < a[i_2]$  then  $b[i_1] := 1$  fi;

- (4) **od**;

- (5) for  $i \in \{1..n\}$  pardo

- (6) **if** b[i] = 0 **then** erg := a[i] **fi**;

- (7) **od**.

- Beispiel 2 (Parallel Prefix): Sei a[1..n] ein Feld mit n Zahlen. Das folgende Programm berechnet alle Präfixe der Form  $s[i] = \sum_{j=1}^{i} a[j], j = 1, \ldots, n$ . Es gilt  $t(n) = O(\log n)$  und p(n) = O(n). Der Algorithmus wurde in [LF80] erstmalig vorgestellt. Er gilt

nicht nur für die Addition, sondern für alle assoziativen Operationen. Die Felder b[1...2n-1] und c[1...2n-1] realisieren Beschriftungen vollständiger binärer Bäume, wobei Element 1 die Wurzel darstellt und ein Element i die Söhne 2i und 2i+1 hat.

```

(1) for x \in \{1..n\} pardo b[n-1+x] := a[x] od;

(2) for i := \log n - 1 downto 0 do

for x \in \{2^i...2^{i+1} - 1\} pardo b[x] := b[2x] + b[2x + 1] od;

(4) od;

(5) c[1] := 0;

(6) for i := 1 to \log n - 1 do

for x \in \{2^i...2^{i+1} - 1\} pardo

(8)

if even(x) then c[x] := c[\frac{x}{2}]

else c[x] := c[|\frac{x}{2}|] + b[x-1]

(9)

fi

(10)

(11)

od

(12) od;

(13) for x \in \{1..n\} pardo s[x] := c[n-1+x] + a[x] od;

```

Beispiel 1 ist nur auf einer CRCW PRAM auszuführen, da in Zeile 3 jeweils n Prozessoren ein Feldelement aus a gleichzeitig lesen und eventuell mehrere Prozessoren ein Element aus b gleichzeitig schreiben. Man kann jedes der Modelle common, arbitrary oder priority write wählen, da gleichzeitig schreibende Prozessoren den gleichen Wert schreiben. Laufzeit und Prozessorzahl sind direkt einzusehen. Die Korrektheit zeigt man wie folgt. Am Ende der Ausführung von Zeile 3 gibt es noch genau ein Element in Feld b mit Wert 0. Gäbe es zwei solcher Elemente mit Indices  $i_1$  und  $i_2$ , so hätte Prozessor  $(i_1,i_2)$  in Zeile 3 eines der beiden Feldelemente mit 1 besetzt. Gäbe es kein solches Element mehr, so könnte man einen Zyklus von Bedingungen  $a[i_j] > a[i_{j+1}]$  konstruieren. Beides führt zum Widerspruch. Das eindeutige Element a[i] mit b[i] = 0 nach Ausführung von Zeile 3 ist das Maximum, da es nach Zeile 3 größer als alle anderen sein muß.

Beispiel 2 kann auf einer EREW PRAM ausgeführt werden. Auch hier können Laufzeit und Prozessorzahl direkt abgelesen werden. Die Korrektheit kann aus den folgenden Behauptungen hergeleitet werden:

- 1. Die Beschriftungen b der Blätter des Baumes enthalten nach Ausführung von Zeile 1 die n Zahlen.

- 2. Nach Ausführung der Zeile 4 enthalten die Beschriftungen b[i] der Knoten i des Baumes die Summe der Beschriftungen b an den Blättern des Unterbaumes, von dem i die Wurzel ist.

3. Nach Ausführung der Zeile 12 enthalten die Beschriftungen c[i] der Knoten i des Baumes die Summe der Beschriftungen b der Blätter, die im Baum links von i liegen.

Der Algorithmus kann so weit verbessert werden, daß nur noch  $p(n) = n/\log n$  Prozessoren benötigt werden. Jeder Prozessor  $i \in \{1 \dots n/\log n\}$  berechnet zuerst sequentiell die Summe a'[i] der Zahlen  $a[i(\log n-1)+1]$  bis  $a[i\log n]$ . Dazu wird Zeit  $O(\log n)$  benötigt. Danach führen die Prozessoren obigen Algorithmus für die  $n' = n/\log n$  Zahlen im Feld  $a'[1 \dots n/\log n]$  aus. Lediglich die letzte Zeile wird zu s'[x] := c[n-1+x] verändert. Dazu benötigen sie Zeit  $t(n') = O(\log n') = O(\log n)$ . Man erhält ein Feld  $s'[1 \dots n/\log n]$  der Präfixe der Zahlen aus a'. Jeder Prozessor i berechnet jetzt sequentiell die Präfixe der Zahlen  $a[i(\log n-1)+1]$  bis  $a[i\log n]$  und addiert zu jedem Präfix s'[i]. Auch hierzu wird Zeit  $O(\log n)$  benötigt. Die Gesamtzeit ist  $t(n) = O(\log n)$ , die Prozessorzahl  $p(n) = O(n/\log n)$ . Der Algorithmus ist optimal. Diese Verbesserung mag den Anschein von "Erbsenzählerei" haben, da sich die Laufzeit t(n) größenordnungsmäßig nicht ändert und sich sogar ungefähr um den Faktor 3 erhöht. Sie erlangt ihre Bedeutung erst im Zusammenhang mit der unten angesprochenen Tatsache, daß die Prozessorzahl P realer Rechner sehr viel kleiner ist als n.

Die beiden Beispiele demonstrieren, wie einfach sich parallele Algorithmen für eine PRAM formulieren und analysieren lassen. Die PRAM bietet also ein sehr komfortables Programmiermodell. Eine Vielzahl von PRAM Algorithmen findet man in [GR88, KR90]. Aus diesem Grunde gab und gibt es viele Versuche, eine PRAM zu realisieren.

#### 2.1.3 Realisierungsansätze

Bei einer Realisierung von PRAMs treten zwei Hauptschwierigkeiten auf:

- 1. Eine reale PRAM hat nur konstant viele Prozessoren, die ideale hat Prozessorzahlen in Abhängigkeit der Eingabegröße.

- 2. Die heutige Technologie kennt keine Speicherbausteine, die mehr als 2 oder 3 Ports in konstanter Zeit bedienen. Man kann den globalen Speicher daher nicht direkt realisieren.

Das erste Problem tritt nicht nur bei der PRAM, sondern bei allen Parallelrechnern auf. Man löst es, indem man auf jedem der N vorhandenen Prozessoren p(n)/N logische Prozessoren simuliert. Jeder der logischen Prozessoren wird durch den Zustand aller von ihm benutzten Register des realen Prozessors einschließlich Stackzeiger, Programmzähler und Statusregister repräsentiert. Man nennt dies den Kontext [PS85]. Zusätzlicher Aufwand entsteht nur, wenn die Simulation eines logischen Prozessors angehalten und die eines anderen fortgesetzt wird. Man spricht hierbei von Kontextwechsel [PS85]. Asymptotisch hat der Kontextwechsel keinen Einfluß auf die Laufzeit eines Programms, da der Kontext jedes logischen Prozessors nur Größe O(1) hat und deshalb auch nur Zeit O(1) zum Laden oder Speichern eines Kontextes benötigt wird. Der tatsächliche Einfluß und eventuelle Unterstützung durch Hardware wird in Kapitel 5.3 diskutiert.

Das zweite Problem löst man, indem man den globalen Speicher in mehrere Module, z.B. N Stück, zerteilt und zwischen Prozessoren und Speichermodule ein Netzwerk schaltet. Da die Knoten bekannter Netzwerke konstanten Grad haben (im Fall des  $\log N$ -dimensionalen Würfels auch  $\log N$ ), hat ein Netzwerk mit N Eingängen und Ausgängen mindestens Tiefe  $\log N$ . Der Zugriff auf den globalen Speicher kann also nicht mehr in konstanter Zeit erfolgen, wie es die Definition der PRAM fordert.

Alle mir bekannten Ansätze zur Realisierung von PRAMs (also von Simulationen auf realistischen Maschinen) folgen diesem Weg und beschreiben, wie der globale Speicher auf die verschiedenen Module verteilt wird, welches Netzwerk und welcher Routing Algorithmus gewählt wird. Danach folgt der Beweis der Korrektheit und der Effizienz der Simulation. Im folgenden Abschnitt werden die bekanntesten Ansätze kurz geschildert und ihre Vor- und Nachteile vorgestellt. Valiant gibt in [Val90b] eine Übersicht der bekannten theoretischen Ergebnisse.

Es soll hier bereits angemerkt werden, daß die Hardware für eine PRAM Realisierung nach dem oben gesagten nicht sehr verschieden von der Hardware für derzeit kommerziell erhältliche Parallelrechner ist. Die Bedeutung dieser Beobachtung ist Gegenstand der Dissertation von Abolhassan [Abo92]. Sie soll hier nicht weiter verfolgt werden.

#### 2.2 Theoretische Vorarbeiten

Bevor nachfolgend einzelne Ansätze kurz geschildert werden, sollen einige grundlegende Entscheidungen begründet werden, die den meisten Ansätzen zugrunde liegen. Die erste Beobachtung betrifft die Art der Verteilung des globalen Speichers auf Module. Der zweite wichtige Punkt ist die Auswahl der Verbindungsstruktur.

#### 2.2.1 Verteilen des globalen Speichers

Die Zeit zur Simulation eines Schrittes einer PRAM ist nach unten beschränkt durch die Tiefe des verwendeten Netzwerkes und durch die maximale Anzahl von Speicherzugriffen, die ein Speichermodul zu bearbeiten hat (Modulbelastung). Ist die Verteilung des globalen Speichers fest und eindeutig in dem Sinne, daß von keiner Zelle des globalen Speichers mehrere Kopien auf verschiedenen Modulen angelegt werden, so kann ein Zugriffsmuster der Prozessoren konstruiert werden, daß die Zugriffe aller N Prozessoren in einem Modul stattfinden. Die Zeit zur Simulation wäre damit linear. Eine lineare Simulationszeit kann aber auch sequentielle Simulation aller Prozessoren auf einem sequentiellen Rechner erreicht werden. Deshalb muß dieser Fall möglichst vermieden werden.

#### Deterministische Verfahren

Deterministische Strategien zur Verteilung des globalen Speichers arbeiten mit mehreren Kopien jeder Speicherzelle. Die Kopien befinden sich auf verschiedenen Modulen. Formal ist die Verteilung durch einen bipartiten Graphen gegeben. Die Teilmengen bestehen aus den zu verteilenden Zellen des globalen Speichers und den Modulen. Eine Kante zwischen einer Zelle und einem Modul bedeutet, daß eine Kopie dieser Zelle auf diesem Modul gehalten wird. Bei einem Zugriff wird stets nur ein Teil (aber mehr als die Hälfte) der Kopien aktualisiert bzw. gelesen. Dies garantiert, daß bei einem Lesezugriff stets mindestens eine aktuelle Kopie gelesen wird. Die Auswahl der Kopien wird abhängig vom Zugriffsmuster so gewählt, daß die Modulbelastung möglichst gering ist.

Unabhängig voneinander zeigten Alt, Hagerup, Mehlhorn und Preparata [AHMP87] und Karlin und Upfal [KU88], daß bei dieser Methode die Simulationszeit eines Schritts mindestens  $\Omega(\log^2 N/\log\log N)$  beträgt. Die beste bekannte Strategie ist die von Bilardi und Herley [BH88], sie benötigt Zeit  $O(\log N\log M/\log\log N)$ . Die Konstante in der asymptotischen Notation ist sehr groß, da eine Sortierung nach Ajtai, Komlós und Szemerédi [AKS83] verwendet wird. Eine verbesserte Version dieses Verfahrens durch Upfal [Upf89] hat nach [Mas90] eine Konstante von 25000. Die deterministischen Verfahren sind deshalb bisher noch nicht von praktischem Nutzen und werden nicht weiter betrachtet.

Anmerkung: Das Verfahren von BILARDI und HERLEY benötigt einen Verteilungsgraphen mit Expandereigenschaft. Die einzige derzeit bekannte Möglichkeit zur effizienten Erzeugung großer Expandergraphen ist das Würfeln. In diesem Sinne ist somit auch dieses Verfahren randomisiert.

#### Randomisierte Verfahren — Hashing

Bei randomisierten Verfahren versucht man durch Verwendung von Zufallszahlen in der Funktion, die den Speicher auf die Module verteilt, die Wahrscheinlichkeit zu begrenzen, daß ein Simulationsschritt lineare Zeit erfordert. Man benutzt die Strategie des universellen Hashings. Universelle Hash-Funktionen wurden von Carter und Wegman eingeführt [CW79]. Bei universellem Hashing benutzt man eine Klasse von Hash-Funktionen, die die Eigenschaft besitzt, daß es für jedes Muster aus disjunkten Adressen und jedes Muster aus Speichermodulen nur sehr wenige Funktionen dieser Klasse gibt, die diese Adressen auf diese Module abbilden. Wählt man vor dem Beginn der Simulation aus einer solchen Klasse eine Hash-Funktion zufällig aus, so ist die Wahrscheinlichkeit sehr klein, daß die Funktion den Speicher so auf die Speichermodule aufteilt, daß die Modulbelastung hoch wird. Mehlhorn und Vishkin benutzen in [MV84] die einfach zu konstruierende Klasse  $\mathcal{H}_s$ :

$$\mathcal{H}_s = \{pol(x) \bmod P \bmod N : pol(x) \text{ ist Polynom vom Grad } s\}.$$

Hierbei ist N die Anzahl der Speichermodule, auf die verteilt werden soll. P ist eine

Primzahl mit  $P \geq N$ . Auch Karlin und Upfal führen diese Klasse ein [KU88]. Bei vorgegebenem Muster und zufälliger Auswahl eines Polynoms dieser Klasse (durch zufälliges Auswählen der Koeffizienten) ist die Wahrscheinlichkeit, daß mehr als s Werte auf ein bestimmtes Modul abgebildet werden, durch  $N^{1-s}$  beschränkt. Man erreicht also mit sehr hoher Wahrscheinlichkeit eine Modulbelastung von höchstens s. Da wegen der Netzwerktiefe von mindestens  $\log N$  die Simulation eines Schrittes mindestens Zeit  $O(\log N)$  benötigt, ist eine Modulbelastung von  $s = \log N$  ausreichend. Man benötigt also Polynome des Grades  $\log N$ . Neuere Forschungen von Dietzfelbinger [Die91b] zeigen, daß sogar Polynome konstanten Grades größer 1 ausreichen, daß jedoch lineare Funktionen den Anforderungen im allgemeinen nicht genügen [Die91a].

#### Lokales Verteilen

Bisher wurde nur die Verteilung des globalen Speichers auf die Module betrachtet. Die Zellen des globalen Speichers jedoch, die auf ein Modul abgebildet werden, müssen noch lokalen Zellen dieses Moduls zugeordnet werden. Hierzu berechnet man erst  $g(x) = pol(x) \mod P \mod M$  und bildet dann die Modulnummer  $h(x) = g(x) \mod N$  und die lokale Adresse l(x) = g(x) div N. Allerdings ist für Polynome eines Grades größer 1 die Funktion g(x) nicht bijektiv, d.h. daß mehrere Zellen des globalen Speichers auf die gleiche Zelle eines Moduls abgebildet werden können. Hier wäre die Benutzung von linearen Funktionen hilfreich. Zusätzlich könnte die Berechnung von g(x) vereinfacht werden, da bei linearen Hash-Funktionen statt einer Primzahl auch eine Zweierpotenz eingesetzt werden kann, bei Polynomen höheren Grades jedoch nicht [Die90]. Die Berechnung "modulo Zweierpotenz" ist im Binärsystem, das von Computern im allgemeinen verwendet wird, in einem Schritt möglich, die Berechnung "modulo Primzahl" jedoch nicht.

Eine einfache Methode zur Bewältigung des Problems wäre eine Vergrößerung der Module um den Faktor Grad des Polynoms, da maximal soviele Zellen des globalen Speichers in eine Zelle eines Moduls abgebildet werden können. Abgesehen davon, daß dies teuer wird, wird auch der Zugriff schwieriger, da bei jeder Zelle eines Moduls gespeichert werden muß, welche Zelle des globalen Speichers auf sie abgebildet wurde.

RANADE gibt ein Verfahren an [Ran91], das lokales Adressieren auch bei Hash-Funktionen realisiert, die nicht bijektiv sind, ohne die Module asymptotisch zu vergrößern, wobei sich auch die Zugriffszeit größenordnungsmäßig nicht ändert. Die Konstanten in zusätzlich benötigtem Speicher und zusätzlicher Zugriffszeit können jedoch nicht vernachlässigt werden.

Da Simulationen [Eng92, RBJ88] darauf hindeuten, daß in der Praxis der Grad der Hash-Funktion kaum Einfluß auf die Simulationszeit hat, werden später lineare Hash-Funktionen verwendet.

#### 2.2.2 Verbindungsstrukturen

Als Verbindungsstrukturen benutzt man Netzwerke. Diese kann man als Graphen G=(V,E) betrachten. Einige der Knoten des Graphen, die sogenannten Sender, können Nachrichten ins Netzwerk einspeisen, einige Knoten, die sogenannten Empfänger, nehmen für sie bestimmte Nachrichten aus dem Netzwerk. Alle Knoten des Netzwerkes, auch die, die weder Sender noch Empfänger sind, übernehmen die Weiterleitung von Nachrichten. Nachrichten werden über die Kanten des Graphen von einem Knoten zu einem anderen weitergeleitet. Sind die Kanten ungerichtet, können sie Nachrichten in beide Richtungen transportieren, sind sie gerichtet, nur in eine Richtung. Jede Kante kann in einer Zeiteinheit nur eine bestimmte Menge an Information transportieren. Der Durchmesser eines Netzwerkes ist der Durchmesser des zugrunde liegenden Graphen. Entscheidende Kriterien eines Verbindungsnetzwerkes sind nach [HB84] die Art der Vermittlung von Nachrichten, die Kontrollstrategie, die Betriebsart und die Topologie des zugrunde liegenden Graphen.

Die beiden wichtigsten Vermittlungsarten von Nachrichten sind Leitungsvermittlung (circuit switching) und Paketvermittlung (packet switching). Bei leitungsvermittelnden Netzwerken wird zwischen den Kommunikationspartnern ein physikalischer Pfad geschaltet, über den die Nachrichten verschickt werden. Die Zeit zum Erstellen des Pfades ist im Allgemeinen größer als die Zeit zum Transport einer Nachrichteneinheit (nach [Mül89] etwa Faktor 100). Bei paketvermittelnden Netzwerken werden die zu versendenden Nachrichten in sogenannte Pakete verpackt, die außer der Nachricht selbst noch Informationen über Sender und Empfänger der Nachricht enthalten. Diese Pakete werden durch das Netzwerk geschickt, ohne daß dazu ein physikalischer Pfad zwischen Sender und Empfänger als ganzes geschaltet werden müßte. Im einfachsten Fall wird das Paket als Ganzes von einem Knoten zum nächsten transportiert (Store-and-Forward Prinzip, [Tan89]). Innerhalb der Knoten werden die Pakete in Queues zwischengespeichert. Es gibt auch Netzwerke, in denen das Paket in mehrere Teile, die sogenannten "Flits", aufgeteilt werden kann (Cut-Through Prinzip, [KK79]). Dort wird zumindest teilweise ein physikalischer Pfad etabliert, dessen Länge mit der Anzahl der Flits variiert. Bei paketvermittelnden Netzwerken wird keine Zeit zum Aufbau eines Pfades benötigt. Die Zeit zum Transport eines Paketes von einem Knoten des Netzwerkes zu einem anderen ist größer als bei einer Leitungsvermittlung, da die Kante, über die das Paket weitertransportiert werden soll, erst aus der Nummer des Empfängers berechnet werden muß und da eventuell mehrere Pakete die gleiche Kante benutzen wollen und nacheinander geschickt werden müssen. Letzeren Fall nennt man einen Konflikt.

Man kann aus oben gesagtem ersehen, daß sich leitungsvermittelnde Netzwerke eher für Anwendungen eignen, bei denen vorwiegend Nachrichten großen Umfangs verschickt werden, paketvermittelnde Netzwerke hingegen eher für Anwendungen, bei denen sehr viele kurze Nachrichten verschickt werden. Eine Nachricht soll hierbei kurz sein, wenn die Größe der Nachricht selbst ungefähr der Größe der Information über Sender und Empfänger entspricht. Bei einer PRAM-Simulation bestehen die Nachrichten aus Anforderungen für Zugriffe auf den globalen Speicher. Sie enthalten nur Informationen über die Art des Zugriffs, die Adresse der betroffenen Speicherzelle und eventuell das zu schreibende Datum, sind also

kurz. Außerdem sind sie häufig. Im weiteren Verlauf der Arbeit werden deswegen nur paketvermittelnde Netze nach dem Store-and-Forward Prinzip betrachtet.

Bekannte Kontrollstrategien sind zentrale und verteilte Kontrolle. Bei einer zentralen Kontrolle berechnet eine Kontrolleinheit die Einstellung aller Knoten abhängig von den Sender/Empfänger-Kombinationen aller auftretenden Nachrichten. Bei einer verteilten Kontrolle berechnet jeder Knoten selbst seine Einstellung abhängig von den Sender/Empfänger-Kombinationen der gerade bei ihm anliegenden Nachrichten, unabhängig von allen anderen Nachrichten. Zentrale Kontrolle findet man in der Regel bei leitungsvermittelnden Netzwerken, oft findet sie off-line statt, d.h. die Berechnung findet nicht zur Laufzeit, sondern schon vorher, zum Beispiel zur Compilezeit, statt. Verteilte Kontrolle findet man bei allen mir bekannten paketvermittelnden Netzwerken. Der Grund hierfür liegt darin, daß die Kante, über die ein Paket weitergeschickt werden muß, sich in der Regel sehr einfach aus der Nummer des Empfängers berechnen läßt. Die Entscheidung, ob dieses Paket weitertransportiert werden kann, hängt nur davon ab, ob ein Konflikt auftritt. Hierzu genügt die Kenntnis der anderen Pakete, die gerade in diesem Knoten vorliegen. Eine verteilte Kontrolle ist also möglich und wegen ihrer Einfachheit auch vorzuziehen. Es ist auch ein leitungsvermittelndes Netzwerk mit verteilter Kontrolle bekannt. Innerhalb des ALEWIFE Projektes am MIT wird in [Kni89] ein solches Netzwerk beschrieben, das nach dem Prinzip des Wormhole Routing [DS87] funktioniert. Da in dieser Arbeit aber keine leitungsvermittelnden Netze betrachtet werden, wird nicht weiter darauf eingegangen. Im Weiteren werden alle betrachteten Netzwerke mit einer verteilten Kontrolle versehen sein.

Als Betriebsarten unterscheidet man synchronen und asynchronen Betrieb. Bei synchronem Betrieb dürfen nur in bestimmten Zeitabständen neue Nachrichten ins Netzwerk eingespeist werden, bei asynchronem Betrieb darf dies zu beliebigen Zeitpunkten geschehen. Synchroner Betrieb kann als Spezialfall des asynchronen Betriebs betrachtet werden, bei dem die Möglichkeit des Einspeisens zu beliebigem Zeitpunkt nicht ausgenutzt wird.

Bei Topologien unterscheidet man regelmäßige und unregelmäßige Netzwerke, innerhalb der regelmäßigen statische und dynamische Netzwerke. Bei statischen Netzwerken ist jeder Knoten ein Sender und Empfänger, bei dynamischen unterscheidet man zwischen Sendern/Empfängern, die in der Regel Prozessoren darstellen, und anderen Knoten, die nur als "Schalter" zur Weiterleitung von Nachrichten (routing switch) dienen. Zu den statischen Netzwerken zählen das eindimensionale Feld (array), der Ring, der Stern (star), der Baum (tree), das k-dimensionale Gitter (k-dimensional mesh), der k-dimensionale Würfel (k-dimensional cube, Hypercube) und der Cube-Connected-Cycle. Zu den dynamischen Netzwerken zählen das Shuffle-Exchange Netzwerk und der Crossbar als Single-stage Netzwerke und das Butterfly Netzwerk, das Baseline Netzwerk und die Clos-Netzwerke [Clo53] als Multistage Netzwerke. Die Netzwerke, die im Verlauf der Arbeit noch benutzt werden, werden im folgenden definiert. Für alle anderen sei auf das bereits erwähnte Buch von Hwang und Briggs [HB84] verwiesen.

Die beiden letzten Kriterien wurden der Vollständigkeit halber aufgenommen. Da im weiteren Verlauf der Arbeit die Unterscheidung zwischen statischen und dynamischen bzw.

synchronen und asynchronen Netzwerken nicht von Bedeutung ist, werden wir die Begriffe nicht weiter verwenden.

#### 2.2.3 Einige Netzwerke

In den folgenden beiden Definitionen werden die den benutzten statischen und dynamischen Netzwerken zugrunde liegenden Graphen definiert.

**Definition 2.2** Das k-dimensionale Gitter mit Seitenlänge s ist ein ungerichteter Graph  $\mathcal{G}_{s,k} = (V_G, E_G)$  mit  $V_G = \{0, \ldots, s-1\}^k$  und  $\{(a_0, \ldots, a_{k-1}), (b_0, \ldots, b_{k-1})\} \in E_G$  dann und nur dann wenn es genau ein  $i \in \{0, \ldots, k-1\}$  gibt mit  $|a_i - b_i| = 1$  und  $a_j = b_j$  für  $j \neq i$ . Man nennt dies die i-te Kante von  $(a_0, \ldots, a_{k-1})$  beziehungsweise  $(b_0, \ldots, b_{k-1})$ . Der k-dimensionale Würfel (Hypercube)  $\mathcal{H}_k$  ist ein k-dimensionales Gitter der Seitenlänge s = 2.

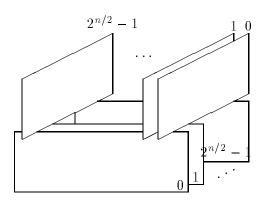

**Definition 2.3** Das s-Butterfly mit Grad 2 ist ein gerichteter Graph  $\mathcal{B}_s = (V_B, E_B)$  mit  $V_B = \{0, \ldots, s\} \times \{0, \ldots, 2^s - 1\}$  und für  $a_0 \in \{0, \ldots, s - 1\}$  ist  $((a_0, a_1), (a_0 + 1, b_1)) \in E_B$  genau dann wenn  $b_1 = a_1$  oder  $b_1 = a_1 \oplus 2^{a_0}$ .

Die Schreibweise  $x \oplus y, x, y \in \{0, \dots, 2^s - 1\}$  ist eine Abkürzung für die Zahl, deren s-stellige Binärdarstellung das bitweise exklusive Oder der s-stelligen Binärdarstellungen der Zahlen x und y ist.

Ich werde die folgenden Sprechweisen benutzen. Bei einem Knoten  $(a_0, a_1) \in V_B$  nennt man  $a_0$  die Spaltennummer und  $a_1$  die Zeilennummer. Alle Knoten mit gleicher Spaltennummer bilden eine Spalte, alle Knoten mit gleicher Zeilennummer bilden eine Zeile. Der Row Leader einer Zeile  $a_1$  ist  $(0, a_1)$ . Kanten, die der ersten Bedingung der Definition genügen, heißen gerade Kanten, Kanten, die der zweiten Bedingung der Definition genügen, heißen kreuzende Kanten.

In einigen Artikeln werden die Spalten 0 und s identifiziert, d.h.  $V_B = \{0, \ldots, s-1\} \times \{0, \ldots, 2^s-1\}$  und bei der Definition der Kanten gilt  $((a_0, a_1), ((a_0+1) \bmod s, b_1)) \in E_B$  falls eine der beiden Bedingungen erfüllt ist. Anschaulich entspricht diese Methode einem "Rundkleben" des Graphen. Es werden auch "umgekehrte Butterfly Netzwerke" betrachtet. Bei diesen ist die zweite Bedingung für eine Kante geändert zu  $b_1 = a_1 \oplus 2^{s-a_0}$ . Anschaulich entspricht diese Methode dem Umdrehen der Kanten und einer umgekehrten Numerierung der Spalten.

Netzwerke wie Baseline, Delta und einige mehr werden nicht definiert. Wu und Feng zeigen in [WF80], daß diese Netzwerke alle äquivalent zum Butterfly Netzwerk sind. Dies bedeutet, daß man das eine Netzwerk durch Permutieren der Ein- und Ausgänge aus dem anderen erhält.

#### 2.2.4 Routingalgorithmen

Dieser Abschnitt soll die Entwicklung von Algorithmen zum schnellen Versenden von Paketen in verschiedenen Netzwerken darstellen. Kriterien zur Beurteilung von solchen Routingalgorithmen sind in diesem Zusammenhang die Laufzeit zum Transport der Pakete L im Vergleich zum Durchmesser des Netzwerkes D, die Anzahl der Pakete S, die in dieser Zeit von ihrem Sender zu ihrem Empfänger transportiert werden können, die maximale Länge Q der in den Knoten benötigten Queues, und bei probabilistischen Algorithmen die Wahrscheinlichkeit, mit der die Ergebnisse erreicht werden. Die Zeit wird in Schritten gemessen, ein Schritt ist die Zeit zum Auswählen eine Paketes in einem Knoten und zum Transport über eine Kante zum nächsten Knoten, falls dies möglich ist.

Ein Routingalgorithmus ist optimal, wenn L = O(D), Q = O(1) und S = |V|. Ein weiteres Kriterium ist die Menge der möglichen Sender/Empfänger Kombinationen. Hier sind nur h-Relationen erlaubt. Dies bedeutet, daß jeder Sender höchstens h Pakete ins Netz sendet und daß jeder Empfänger höchstens h Pakete erhält. Es gilt dann h < L. Den Spezialfall h = 1 nennt man Permutation. In unserem Fall ist jedoch der Fall  $h = \log |V|$  von größerer Bedeutung, da auch bei sehr gutem Hashing die Modulbelastung  $\log N$  betragen kann und die Speichermodule hier gerade die Empfänger sind. Desweiteren folgt, daß die Zahl der Sender und die der Empfänger durch |V|/h nach oben beschränkt ist.

Ein erster Durchbruch für das Routen von Permutationen war Valiant's probabilistischer Algorithmus für den k-dimensionalen Würfel [Val82]. Der Algorithmus arbeitet in 2 Phasen. In der ersten Phase wird für jedes Paket ein Zwischen-Empfänger zufällig gewürfelt und das Paket dorthin geschickt. In der zweiten Phase werden die Pakete von den Zwischen-Empfängern zu den Empfängern geschickt. Der Pfad von einem Sender A zu einem Empfänger B wird dabei folgendermaßen gewählt. Man erzeuge einen Bitstring  $a_0, \ldots, a_{k-1}$  der Länge k als bitweises exklusives Oder von A und B. Man suche  $j = \min\{i | a_i = 1\}$ , setze  $a_j = 0$  und schicke das Paket über die j-te Kante von A nach A'. Dort verfährt man ebenso. Das Paket hat B erreicht, wenn  $a_0, \ldots, a_{k-1}$  nur noch Nullen enthält. Bei Konflikten wird eines der Pakete in einer Queue gespeichert, der Algorithmus funktioniert für alle Queue Disziplinen wie First-In-First-Out, Last-In-First-Out usw.

Valiant bewies, daß mit Wahrscheinlichkeit mindestens  $1-2^{-O(k)}$  nach L=O(k) Schritten alle  $S=2^k$  Pakete bei ihrem Empfänger angekommen sind. Die Queues der Knoten können eine Länge von Q=O(k) erreichen. Da der Durchmesser eines Hypercubes D=k ist, sind L und S optimal, nicht jedoch Q.

In der Folge wurden eine Reihe von Routing Algorithmen für Hypercube und ähnliche Netzwerke wie Butterfly oder Shuffle-Exchange Netzwerk entwickelt [Ale82, Upf82, Pip84], die jedoch alle nicht optimal waren, da sie nur für Permutationen gedacht waren. Der erste optimale Algorithmus stammt von Ranade [Ran91, RBJ88], er wurde von Leighton, Maggs und Rao verallgemeinert [LMRR90, LMR88].

Auch für Gitter wurden eine Reihe von Routing Algorithmen entwickelt [KRT88, Kun88,

KT89, LMT89]. Diese sind aber alle nur für Permutationen geeignet und deshalb nicht optimal in unserem Sinne.

Die beste Lösung bietet der Algorithmus von RANADE, da er auch die Behandlung von konkurrierenden Zugriffen mit einschließt. Seine Lösung umfaßt außerdem sowohl Hashing als auch Routing, deshalb soll diese Lösung im nächsten Abschnitt weiter entwickelt werden.

#### 2.3 Die Fluent Machine

Ranade veröffentlichte 1987 einen probabilistischen Algorithmus [Ran87], der auf einem n-Butterfly Netzwerk arbeitet und  $N=n2^n$  Pakete mit Wahrscheinlichkeit mindestens  $1-2^{-O(n)}$  in Zeit O(n) routet und nur Knoten mit Queues der Länge O(1) benötigt. Der Algorithmus ist damit optimal. Sender und Empfänger sind alle Knoten des Butterfly Netzwerkes. Jeder Sender sendet ein Paket, die Empfänger der Pakete können beliebig gewählt werden. Ranade benutzte diesen Algorithmus zum Entwurf der sogenannten "Fluent Machine" [RBJ88], die eine PRAM schrittweise simuliert. An jedem Knoten des Butterfly Netzwerkes befinden sich ein Prozessor und ein Speichermodul. Ein Prozessor sendet am Anfang eines Schrittes ein Paket ins Netzwerk, wenn er in diesem Schritt einen Zugriff auf den globalen Speicher simuliert. Der Algorithmus unterstützt konkurrierendes Lesen und Schreiben von Zellen. In den folgenden Abschnitten wollen wir die Verteilung des globalen Speichers und den Algorithmus beschreiben.

#### 2.3.1 Verteilung des globalen Speichers

Die Verteilung erfolgt mittels Hashfunktionen in folgender Art und Weise. Die Speicherzelle  $x \in \{0, ..., m-1\}$  des globalen Speichers wird im Speichermodul  $h(x) = g(x) \mod N$  an Adresse l(x) = g(x) div N abgelegt. g(x) wird zufällig aus der Menge G gewählt:

$$G = \left\{ g | g(x) = \left( \sum_{0 \le i < \zeta} a_i x^i \right) \bmod P \right\}$$

Hierbei ist  $P \geq m$  eine Primzahl und die Koeffizienten  $a_i \in \{0, \ldots, P-1\}$ . Die Variable  $\zeta$  wird zu  $\zeta = 8n$  gewählt. Die Funktion g ist also im allgemeinen nicht bijektiv. Bis zu  $\zeta$  verschiedene Adressen können mittels g auf eine abgebildet sein. Eine einfache Methode, um dieses Problem zu lösen ist die folgende. Jede der m/N Zellen pro Modul wird durch  $2\zeta$  viele Zellen ersetzt. Die ersten  $\zeta$  dieser Zellen erhalten die Originaladressen, die auf diese Zelle abgebildet wurden, die anderen die Inhalte dieser Zellen. Dadurch wird allerdings der Gesamtspeicher um den Faktor  $2\zeta = 16n$  vergrößert. Ranade skizziert in [Ran87] eine Methode, die diesen Faktor zur Konstante reduziert. Da im weiteren Verlauf an Stelle dieser Hashfunktion eine lineare (und damit bijektive) Funktion verwendet wird, wird auf die Schilderung dieser Lösung verzichtet. Siehe hierzu auch Absatz 2.2.1.

Die Modulnummer h(x) einer Zelle des globalen Speichers ist ein Wert aus  $\{0, \ldots, N-1\}$ , die Knoten des Butterfly Netzwerkes, die Module tragen, sind allerdings Werte aus  $\{0, \ldots, n-1\} \times \{0, \ldots, 2^n-1\}$ . Zur Umsetzung wird die Bijektion  $h'(x) = (x \text{ div } 2^n, x \text{ mod } 2^n)$  benutzt. Im Rest dieses Kapitels wird aus Gründen der Einfachheit in der Regel h(x) dem exakten h'(h(x)) vorgezogen.

#### 2.3.2 Routing

Will ein Prozessor einen Zugriff auf eine Zelle x des globalen Speichers machen, so schickt er ein Paket ins Netzwerk. Ein solches Paket besteht aus der Adresse x, der gehashten Adresse h(x), einem Typ, der die Art des Zugriffs (lesend oder schreibend) angibt und bei einem schreibenden Zugriff aus dem zu schreibenden Datum. Wir werden im folgenden nur Lesezugriffe betrachten. Schreibzugriffe werden genauso behandelt mit der Vereinfachung, daß hier kein Ergebnis zum Prozessor zurückgeschickt werden muß.

Der Algorithmus arbeitet in 6 Phasen. Zur einfacheren Beschreibung wollen wir vorerst annehmen, daß das benutzte Netzwerk aus 6 aneinandergehängten Butterfly Netzwerken besteht, von denen die mit gerader Nummer umgekehrt sind. Unter Aneinanderhängen von Netzwerken verstehen wir hier, daß die Spalte n des Netzwerkes i mit Spalte 0 des Netzwerkes i+1 identifiziert wird.

Jeder Netzwerkknoten hat 2 eingehende und zwei ausgehende Kanten. Pakete, die über eine eingehende Kante den Knoten erreichen, werden in Puffern gespeichert, die maximal b Pakete beinhalten können. Die Puffer arbeiten nach dem First-in-First-out Prinzip. Pakete dürfen über eine ausgehende Kante nur verschickt werden, wenn der betreffende Eingangspuffer des Nachfolgeknotens nicht voll ist.

Ein Paket, das von einem Prozessor  $(a_0, a_1)$  ausgeschickt wird und zum Speichermodul  $h(x) = (b_0, b_1)$  will, benutzt den folgenden Pfad:

- 1. In Phase 1 folgt es von  $(a_0, a_1)$  dem Pfad der geraden Kanten nach  $(n, a_1)$ , der gleichzeitig  $(0, a_1)$  der Phase 2 ist.

- 2. In Phase 2 folgt das Paket dem eindeutigen Pfad von  $(0, a_1)$  nach  $(n, b_1)$  der Phase 2, der gleichzeitig  $(0, b_1)$  der Phase 3 ist.

- 3. In Phase 3 folgt das Paket von  $(0, b_1)$  dem Pfad der geraden Kanten nach  $(b_0, b_1)$ . Dort findet der Speicherzugriff statt.

- 4. 6. In diesen Phasen läuft das Antwortpaket genau den gleichen Pfad wie auf dem Hinweg in umgekehrter Reihenfolge.

In Abbildung 2.1 ist der Weg eines Paketes über alle 6 Phasen dargestellt. Der Knoten  $(a_0, a_1)$  ist dort mit Source, der Knoten  $(b_0, b_1)$  ist mit Destination bezeichnet. Die Abbildung zeigt auch, daß das Paket in den Phasen 1, 3, 4 und 6 nur über gerade Kanten

Abbildung 2.1: 6 Phasen Routing der Fluent Machine

weitertransportiert wird. Nur in den Phasen 2 und 5 werden also die kreuzenden Kanten zum Transport von Paketen im Netzwerk benutzt. In Phase 1 benutzen die Prozessoren die kreuzenden Kanten, um die Pakete ins Netzwerk einzuspeisen. Die kreuzenden Kanten enden in Phase 1 also zwar in einem Netzwerkknoten, ihr Anfang ist aber mit einem Prozessor verbunden. In Phase 3 hängt am Ende von kreuzenden Kanten ein Speichermodul, über diese Kanten laufen die Pakete, wenn sie ihren Zielknoten erreicht haben, um den Speicherzugriff auszuführen. In Phase 4 speisen die Speichermodule über die kreuzenden Kanten die Antworten von LOAD Paketen wieder ins Netzwerk ein. In Phase 6 hängt an ausgehenden kreuzenden Kanten ein Prozessor. Hier werden die Pakete, die ihren Ausgangsprozessor wieder erreicht haben, über die kreuzenden Kanten aus dem Netzwerk ausgespeist.

#### 2.3.3 Konkurrierende Zugriffe

Erfolgt in einem Schritt der zu simulierenden PRAM ein konkurrierender Zugriff auf eine Adresse x, so schicken mehrere Prozessoren bei der Simulation dieses Schrittes Pakete mit gleichen Originaladresen x und damit gleichen gehashten Adressen h(x) ins Netz. Die Pfade dieser Pakete bis zum Speichermodul h(x) bilden einen Baum im Netzwerk. Allerdings ist es nicht notwendig, mehr als ein solches Paket über jede Kante des Baumes zu senden. Um dies zu erreichen, muß man dafür sorgen, daß sich nicht nur die Pfade dieser Pakete, sondern die Pakete selbst treffen. Treffen sich zwei solche Pakete in einem Knoten, so können sie zu einem kombiniert werden. Bei lesendem Zugriff kann ein Paket gelöscht werden, allerdings muß gewährleistet sein, daß das übriggebliebene Paket auf dem Rückweg an entsprechender Stelle wieder dupliziert wird. Bei schreibendem Zugriff wird das Paket gelöscht, das von einem Prozessor kleinerer Nummer kommt, wodurch eine Priority Regelung realisiert wird. Die Idee der Kombinierung von Paketen wird bereits beim Design des NYU Ultracomputers beschrieben [GGK<sup>+</sup>83].

Um zu gewährleisten, daß sich zu kombinierende Pakete auch wirklich treffen, verlangt der Algorithmus, daß die Pakete, die einen Knoten verlassen, nach ihren gehashten Adressen aufsteigend sortiert sind. Deshalb erfolgt die Auswahl, welches der beiden führenden Pakete der beiden Eingangspuffer eines Knotens weitergeschickt werden soll, über die gehashten Adressen der beiden Pakete. Das Paket mit der kleineren Adresse darf zuerst weiter, das

andere muß warten. Ist ein Eingangspuffer leer, so muß das führende Paket des anderen Eingangspuffers warten. Unter der Annahme, daß die Pakete in den Eingangspuffern eines Knotens sortiert eintreffen, verlassen sie den Knoten auch sortiert. Durch Induktion über die Spalten des Netzwerks läßt sich nun beweisen, daß die Auswahl den Anforderungen des Algorithmus genügt.

Treffen sich also die Pfade zweier zu kombinierender Pakete, so befinden sich beide Pakete zu gleicher Zeit an den Spitzen der beiden Eingangspuffer und können kombiniert werden. Die Gegenannahme führt direkt zum Widerspruch zur Voraussetzung, daß die von diesem Knoten ausgehende Folge von Paketen nach Adressen aufsteigend sortiert ist. In diesem Fall würden die beiden Pakete nämlich nacheinander den Knoten verlassen und dazwischen mindestens ein anderes Paket mit gehashter Adresse  $h(y) \neq h(x)$ . Die Folge h(x), h(y), h(x) ist aber nicht aufsteigend sortiert.

Erfolgen in einer Runde sowohl lesende als auch schreibende Zugriffe auf eine Adresse x, so werden nur Pakete gleichen Typs kombiniert. Treffen Pakete für Adresse x und verschiedenen Zugriffsarten aufeinander, so hat das Paket mit lesendem Zugriff Vorrang. So lesen alle Prozessoren, die lesenden Zugriff auf Adresse x haben, noch den alten Wert, der neue Wert wird erst später, aber noch in der Simulation des gleichen PRAM Schrittes geschrieben.

#### 2.3.4 Ghost Pakete

Die Idee, die Pakete nach Adressen sortiert zu halten, hat einen großen Nachteil. Betrachtet man Abbildung 2.2, die aus [Ran87] entnommen ist, so stellt man fest, daß das Paket mit Adresse 25 nicht versendet werden kann, weil der andere Eingangspuffer leer ist, obwohl über die Kante von Knoten A nach B in diesem Schritt wegen der Sortierung nie mehr ein Paket mit einer Adresse kleiner als 35 kommen kann. Um solche unnützen Wartezeiten zu vermeiden, sendet ein Knoten, der ein Paket über eine ausgehende Kante verschickt, über die andere ausgehende Kante ein Paket mit gleicher Adresse und Typ Ghost. Dieses Ghost Paket informiert den nachfolgenden Knoten, in unserem Beispiel B, daß kein Paket mit kleinerer Adresse mehr kommen kann. So könnte im Fall der Abbildung 2.2 das Paket in B versendet werden.

Ein Ghost Paket würde auch von A nach B geschickt, wenn das Paket mit Adresse 35 nicht über die ausgehende Kante versendet werden könnte, weil der daran hängende Eingangspuffer des nachfolgenden Knotens voll wäre. Damit sendet jeder Knoten, nachdem er zum ersten Mal ein Paket ausgesandt hat, in jedem Schritt über jede Kante ein Paket, falls nicht der betreffende Eingangspuffer im nachfolgenden Knoten voll ist. Ein Paket muß also in einem Knoten nur noch warten, wenn wirklich die Möglichkeit besteht, daß noch ein anderes Paket vor ihm diesen Knoten verläßt.

Ein Ghost erfüllt seinen Zweck allerdings nur, wenn er im nächsten Schritt auch wirklich versandt werden kann. Steht in dem Eingangspuffer, in den er gerade aufgenommen wurde, noch mindestens ein Paket vor ihm, so kann er im nächsten Schritt nicht verschickt werden.

Abbildung 2.2: Funktion von Ghost Paketen

In diesem Schritt trifft aber wieder ein Paket mit einer nicht kleineren Adresse ein. Gleiches gilt für ein Ghost Paket an der Spitze eines Eingangspuffers, das nicht versandt wird, weil der nachfolgende Eingangspuffer voll ist, oder weil an der Spitze des anderen Eingangspuffers ein Paket mit kleinerer Adresse steht. Solche Ghost Pakete werden gelöscht.

Ghost Pakete halten das Netzwerk "fluent", daher der Name der Maschine. Eine ähnliche Funktion haben "End Of Stream" Pakete (EOS). EOS Pakete haben den Typ Ghost, aber als Adresse m. Jeder Prozessor schickt ab dem Zeitpunkt, zu dem er ein Paket ins Netzwerk geschickt hat, ständig EOS Pakete ins Netz. EOS Pakete verlassen aufgrund ihrer Adresse einen Knoten nur, wenn er kein Paket und keinen Ghost mehr enthält und damit auch nicht mehr erhält. Dies garantiert, daß das letzte Paket, das einen Knoten verläßt, nicht aufgrund eines leeren Eingangspuffers hängenbleibt.

#### 2.3.5 Rückweg

Erreicht ein Paket sein Speichermodul und hat einen Lesezugriff ausgeführt, so muß es wieder zurück zu dem Prozessor, von dem es ausgeschickt wurde. Dies könnte prinzipiell genauso geschehen wie auf dem Hinweg, allerdings gibt es eine einfachere Methode. Jeder Netzwerkknoten in den Phasen 1 bis 3 merkt sich in einem zusätzlichen FIFO Puffer, der sog. "Direction Queue", für jedes Paket, das einen Lesezugriff ausführen will und ihn verläßt, aus welchem Eingangspuffer es kam und über welche ausgehende Kante es den Knoten verließ. Wurde eine Kombinierung zweier Pakete mit Lesezugriffen ausgeführt, so merkt sich der Knoten die Kombinierung und über welche ausgehende Kante das übriggebliebene Paket den Knoten verließ. Ein Knoten der Phasen 4 bis 6 liest jetzt den führenden Eintrag der Direction Queue, wartet bis eine Antwort über die entsprechende Kante zurückkommt, dupliziert diese falls notwendig und schickt die Antwort bzw. die Antworten weiter, wie es der Eintrag vorschreibt.

Da die Direction Queue nur 6 Fälle erfassen muß (Eingang i nach Ausgang  $j, i, j \in \{0, 1\}$

und Kombinierung nach Ausgang  $j, j \in \{0, 1\}$ ), muß sie bei kompakter Kodierung nur 3 Bit breit sein. Da die Laufzeit zur Simulation mit sehr großer Wahrscheinlichkeit höchstens O(n) Schritte dauert, benötigt die komplette Direction Queue O(n) Bits. Da eine Adresse eines Paketes ein Wert aus  $\{0, \ldots, m-1\}$  ist, benötigt ein Paket mindestens  $\Omega(\log m) = \Omega(n)$  Bits zu seiner Kodierung, da  $m \geq N = n2^n$ . Da ein Eingangspuffer konstant viele Pakete enthält, benötigt er  $\Omega(n)$  Bits. Die Direction Queue benötigt also nicht mehr Platz als ein Eingangspuffer, obwohl sie eine größere Länge hat.

In den seltenen Fällen, in denen die Simulation länger als O(n) Schritte dauert, könnte die Direction Queue mehr Platz benötigen. Hier muß dafür gesorgt werden, daß die Queue nicht überläuft. Ist die Direction Queue eines Netzwerkknotens voll, so wird das nächste LOAD Paket, das diesen Knoten auf dem Hinweg durchläuft und deshalb etwas in diese Queue schreiben müßte, so lange aufgehalten, bis die Direction Queue nicht mehr voll ist. Dies beeinträchtigt die Korrektheit des Verfahrens nicht. Die zusätzlich auftretende Verzögerung wird hingenommen, da die Simulation ohnehin Zeit  $O(2^n)$  benötigen kann.

#### 2.3.6 Aufbau

Zur Realisierung der Fluent Machine hängt man ein Butterfly Netzwerk und ein umgekehrtes Butterfly Netzwerk an beiden Enden aneinander. Das erste Netzwerk simuliert die Phasen 1,3,5, das zweite die Phasen 2,4,6. Jeder Netzwerkknoten realisiert drei verschiedene Netzwerkknoten und benötigt deshalb 3 Direction Queues. Da aber zu jedem Zeitpunkt nur eine der drei Phasen in einem Knoten abläuft, müssen die Eingangspuffer nicht verdreifacht werden. Allerdings kann ein Eingangspuffer oder ein Ausgang eines Knoten in verschiedenen Phasen mit verschiedenen Dingen (anderem Knoten, Prozessor, Speichermodul) verbunden sein.

Der Grund, weshalb man als zweites Netzwerk ein umgekehrtes Butterfly Netzwerk benutzt, liegt bei den Direction Queues. Ein naheliegender Aufbau der beiden Netzwerke ist, Knoten  $(a_0, a_1)$  des ersten Netzwerkes und Knoten  $(n - a_0, a_1)$  des zweiten Netzwerkes räumlich direkt nebeneinander anzuordnen, um eine einfachere Verdrahtung zu erhalten. Dies sind allerdings die Knoten, zwischen denen Direction Queues bestehen. Diese können dann sehr einfach realisiert werden.

## Kapitel 3

## Bewertung von Rechnern

In diesem Kapitel wird ein formales Modell zur Beschreibung und Bewertung von Rechnern vorgestellt. Das Modell wurde von MÜLLER und PAUL entwickelt [MP90] und in [Mül91] ausgearbeitet. Es war vorrangig zur Bewertung und zum Vergleich von Prozessoren gedacht, so zum Beispiel zur Beantwortung von Fragen der Art "Sollten in einem RISC Prozessor Ausdrücke besser auf dem Stack oder nach Möglichkeit in den Registern ausgewertet werden?" oder "Sollte man in einen Motorola MC68000 besser einen Carry—Lookahead Addierer oder einen Carry Chain Addierer einbauen?". Die Beantwortung solcher Fragen (und damit der Entwurf neuer Rechner) wird mit diesem Modell von einer Kunst zu einer mathematischen Optimierungsaufgabe. Der erste Abschnitt erläutert das Modell in der hier benötigten Tiefe. Im zweiten Abschnitt werden Änderungen in Zielsetzung und Modell beschrieben, die zum Vergleich von skalierbaren Parallelrechnern notwendig sind. Im dritten Abschnitt werden Standardkomponenten von Rechnern, z.B. Addierer, als Beispiele aufgeführt, im vierten Abschnitt wird die Fluent Machine bewertet.

#### 3.1 Formales Modell

In dem verwendeten formalen Modell werden Architekturen beschrieben. Zu einer Architektur zählt hierbei aber nicht nur die Hardware einer bestimmten Maschine. Auch die Software spielt eine erhebliche Rolle. Da in der Anwendungsprogrammierung heute generell Hochsprachen wie PASCAL oder C benutzt werden, sollte also zumindest der (oder die) benutzte(n) Compiler ebenfalls dazuzählen. Auf die Integration des Betriebssystems und der Peripheriehardware in die Architektur wird verzichtet.

**Definition 3.1** Eine Architektur A wird dargestellt durch ein Tupel  $\mathcal{A} = (IS, H, L, Co)$ . Hierbei ist IS eine Maschinensprache, H eine Hardware, auf der IS ausführbar ist, L eine Menge von Hochsprachen und Co eine Menge von Compilern, die Programme, die in Hochprachen aus L geschrieben sind, in Programme in IS übersetzen.

**Anmerkung:** Wir werden uns im weiteren auf Architekturen mit nur einer Hochsprache beschränken und die einelementigen Mengen L und Co mit ihrem Element identifizieren.

Zu gegebenen IS und H kann für jede Instruktion  $I \in IS$  eine Ausführungszeit  $T_H(I)$  angegeben werden, ferner können die Kosten C(H) der Hardware bestimmt werden. Vorgehensweisen zum schnellen Berechnen von C und T per Hand werden in 3.1.2 formal beschrieben.

Zur Bewertung einer Architektur benötigt man Angaben über die Workload, also ein Modell des Benutzerverhaltens in dem Sinne, wie der Anwender die Ressourcen der Maschine auslastet. Die Workload wird durch ein kurzes Programm B in der Sprache L einschließlich einer Eingabe beschrieben. B heißt Benchmark. Das Problem, geeignete Benchmarks zu finden, ist in der Literatur vielfach behandelt worden. Für einige Fälle konnte man sich auf "Standardbenchmarks" einigen, so zum Beispiel auf die Livermore Loops [McM88] als Benchmarks für Vektorrechner.

Compiliert man B mit Co in ein Programm in der Maschinensprache IS und analysiert man dieses, so erhält man für jede Instruktion  $I \in IS$  ihre absolute Häufigkeit  $H_B(I)$ . Die Vorgehensweise bei Übersetzung und Analyse (ohne den Compiler zu implementieren) ist in 3.1.1 angegeben. Die Gesamtzeit zur Ausführung des Programmes ist dann

$$T_H(B) = \sum_{I \in IS} H_B(I) \cdot T_H(I)$$

.

Der Reziprokwert von  $T_H(B)$  ist ein Maß für die Leistung der Maschine.

Für eine gegebene Architektur A und gegebenes Benchmark B können nun verschiedene Gütemaße G(A, B) definiert werden. Sind Architektur und Benchmark bekannt, können die Indices entfallen. Das Aussehen des Gütemaßes hängt von der Zielsetzung des Architekten ab. Die 3 vorherrschenden Zielsetzungen sind:

Leistung um jeden Preis. Diese Zielsetzung kommt in der Regel nur bei Höchstleistungsrechnern vor. Hier wählt man G = 1/T.

Gutes Preis/Leistungsverhältnis. Diese Zielsetzung ist die gängigste bei "normalen" Computern. Hier wählt man  $G = 1/(T \cdot C)$ .

Leistung wichtiger als Preis. Diese Zielsetzung ist ein Kompromiß zwischen den beiden ersten. Hier wählt man  $G = 1/(T^i \cdot C)$  mit i > 1. Je größer i, desto wichtiger wird die Leistung. In [Mül91] wird hier i = 2 benutzt.

Wir werden im folgenden immer das zweite Gütemaß benutzen.

Die Fragen, die zu Beginn des Kapitels gestellt wurden, kann man mit Hilfe dieses Modells lösen. Man vergleicht dazu zwei Architekturen, die sich im ersten Fall nur im verwendeten Compiler unterscheiden und im zweiten Fall leicht verschiedene Hardware haben. Viele Design-Entscheidungen in der Rechnerarchitektur können jetzt als Optimierungsproblem gelöst werden. Als Beispiel diene die Frage "Welches ist die beste Registerzahl für eine ansonsten fest vorgegebene Architektur A und gegebenes Benchmark B?". Man erhält abhängig von der Zahl x der Register verschiedene Kosten und Laufzeiten. Die Güte G ist damit eine Funktion mit der Variablen x. Gesucht ist der absolute (oder zumindest ein guter lokaler) Maximumpunkt für G(x).

# 3.1.1 Hochsprache und Compiler

Die meisten heutigen Hochsprachen wie PASCAL oder C unterstützen sehr viele verschiedene Anweisungen. Compiler von Hochsprachen nach Maschinensprachen hingegen verfolgen meist nur wenige Strategien und erzeugen nur wenige verschiedene Code-Sequenzen [Mül91]. Ein Beispiel für eine Strategie ist die Ausdrucksauswertung. Hier gibt es die Möglichkeit, Ausdrücke möglichst in den Registern auszuwerten, auf dem Stack oder in einem festen Speicherbereich, dem Scratch.

Ein Compiler für eine weitere Hochsprache oder für eine veränderte Maschine kann also sehr einfach durch Veränderung der Strategien (falls notwendig) und der Code-Sequenzen beschrieben werden. Die Übersetzung eines Hochsprachenprogrammes besteht nun aus der Zerlegung in Code-Sequenzen. Eine Analyse des so entstandenen Maschinenprogramms ist einfach, da die Eingabe des Programms bekannt ist.

# 3.1.2 Hardware

Eine bereits seit Jahrzehnten bekannte Darstellungsform für Hardware ist die Darstellung durch Schaltkreise. Die Schaltelemente oder Komponenten bilden hierbei die Knoten eines gerichteten Graphen, ihre Verbindungen die Kanten. Gewisse Verschaltungsregeln müssen beachtet werden, so zum Beispiel maximaler Ingrad der verschiedenen Typen von Komponenten. Ausgezeichnete Knoten sind Eingänge (Ingrad 0) und Ausgänge (Outgrad 0). Jeder Typ von Komponente (in der Regel die verschiedenen Arten von Gattern) hat gewisse Kosten und eine gewisse Durchlaufzeit (Delay). Die Kosten eines solchen Schaltkreises sind die Summe der Komponentenkosten. Die Durchlaufzeit eines Pfades von einem Eingang zu einem Ausgang ist die Summe der Durchlaufzeit eines Pfades von einem Eingang zu einem Ausgang.

Computer lassen sich mit dem Modell des Schaltkreises allerdings nicht zufriedenstellend beschreiben, da Computer auch Komponenten wie Register, Speicher und Treiber beinhalten. Register können zu Zyklen im Graphen führen, Treiber zu Uneindeutigkeiten (mehrere Treiber führen zu einem Bus), außerdem benötigen beide Kontrollsignale.

Das Modell des Schaltkreises wird deshalb wie folgt zum Begriff der Hardware erweitert.

Abbildung 3.1: Grobstruktur der Hardware

Die Beschreibung der Hardware ist eine verkürzte Form der Beschreibung in [Mül91].

**Definition 3.2** Die Hardware H einer Architektur besteht aus den Datenpfaden DP, der Kontrollogik KON, dem Speichersystem M und den sie verbindenden Bussen. Datenpfade und Kontrollogik werden zur CPU zusammengefaßt. Zur Erläuterung dient Abbildung 3.1.

Um die Kontrollsignale zu berechnen, empfängt KON über CIN einige Daten aus DP. DP und M werden über CDP und CM gesteuert. Der Datenaustausch zwischen DP und M wird über den bidirektionalen Datenbus D und den Adressbus A abgewickelt.

## Grundbausteine

Wir beschreiben zuerst die Grundbausteine der Hardware und die Regeln ihrer Verschaltung. Signale können hierbei Werte aus der Menge  $E = \{0, 1, ?\}$  sein, wobei "?" einen undefinierten Wert bedeutet. Ein Signal heißt aktiv bei Wert 1, inaktiv bei Wert 0.

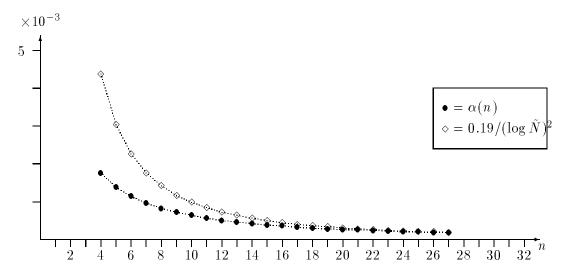

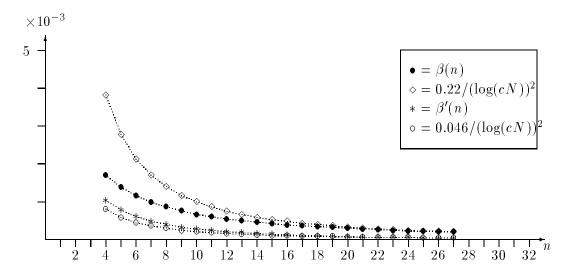

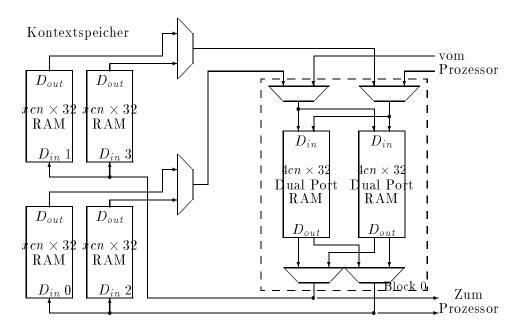

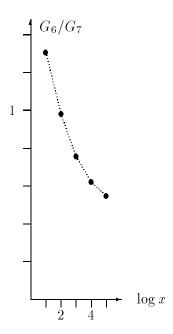

Als Grundbausteine stehen AND, OR, NOR, NAND, EXOR, EQUAL, NOT, Treiber, Register, RAM, ROM und Tristate-Busse zur Verfügung. In der Schaltkreistheorie sind die von den Bausteinen AND bis NOT berechneten Schaltfunktionen nur auf den Signalwerten 0 und 1 definiert. Zur Erweiterung auf die Menge E definiert man den Wert der Schaltfunktion von EXOR, EQUAL und NOT als undefiniert "?", sobald mindestens ein Eingang undefiniert ist. Bei OR (NOR) hat die Schaltfunktion den Wert 1 (0), falls ein Eingang undefiniert ist und der andere den Wert 1 hat, sonst ist der Wert undefiniert. Bei AND (NAND) hat die Schaltfunktion den Wert 0 (1), falls ein Eingang undefiniert ist und der andere den Wert undefiniert.